# AN APPROACH TO THE INCREASE OF THE PERFORMANCE OF VLSI SYSTEM BY IMPLEMENTING SYSTOLIC ARRAY

### 楊立人

(作者為本校應用數學系兼任講師)

# 摘 要

本文主要是研究有關電腦中微處理機內部資料傳送之另一簡捷方法。當初美國卡內基——梅隆大學(Carnegic-Mellon University)電腦系孔教授(Prof. H. T. KUNG)之所以取收縮陣列來做此種傳送方法之名是因爲此種處理方法有如人體心臟之跳動,十分有節奏一放一縮的運作著。

有關收縮陣列方面之論著已不在少數,但直至目前爲止,彼等之解決方法大致只能將  $(n+1) \times (n+1)$  之線性方程式系統所用之傳輸時間減至 Bareiss 所提出之 Order  $(n^2)$  或 Bitmead & Anderson所提出的 Order  $(nlog^2n)$ 。如果 n 值不大,Order  $(nlog^2n)$ 所花的時間會較長,換句話說,即其速度反而會比 Order  $(n^2)$  要來得慢,同時其解法也比較繁複。

據本文以 Bareiss 所提出之解法做修正並推衍之結果,吾人理論上似可利用一維之收縮陣列將超大型電腦之線性方程式系統使用之時間與記憶空間具減為 Order(n)。

#### ABSTRACT

A systolic system is a network of processors which rhythmically compute and pass data through the system. Many basic matrix computations can be pipelined efficiently on systolic networks having an array structure. In this paper we are trying to find a better solution for an  $(n+1) \times (n+1)$  system of linear equations by using a one-dimensional systolic array. In the algorithms implemented shown that it requires only order(n) time and order(n) storage.

### 1. Introduction

Systolic array has been used so widely during the recent years in solving different problems occured or being found in the VLSI system. Charles E. Leiserson proposed a systolic priority queues in the VLSI circuits, H.T. Kung has designed algo-

rithms for VLSI chips. Recently Bitmead and Anderson proposed procedures which require only order  $(nlog^2n)$  time and order(n) space when applied to order(n+1) system. We found that these procedures are kind of too complicated and if n is not really large then its speed would be even slower than the  $order(n^2)$ -time methods which has been proposed by Bareiss. In order to find a better solution which can compete with the previous researches, we have implemented and modified Bareiss algorithms which have been proved requires only O(n) processors. The results we have got are quite excited. After the new implementations, we have reduced the storage requirements from  $O(n^2)$  down to O(n).

### 2. Brief Review of the Bariess Algorithm

At the beginning, let us review some of the algorithms developed by Bariess. Suppose there is a matrix of order(n+1) and we named it as T which respond to a column vector B. In short, it is Tx = B, and after extension, it becomes

$$\begin{bmatrix} t_0 & t_1 & t_2 & - & - & - & - & - & - & t_n \\ t_{-1} & t_0 & t_1 & - & - & - & - & - & - & t_{n-1} \\ t_{-2} & t_{-1} & t_0 & - & - & - & - & - & - & t_{n-2} \\ \vdots & \vdots & \ddots & \ddots & \ddots & \ddots & \ddots & \ddots \\ \vdots & \vdots & \ddots & \ddots & \ddots & \ddots & \ddots & \ddots \\ t_{-n} & t_{-n+1} & t_{-n+2} & \ddots & \ddots & \ddots & \ddots & t_0 \end{bmatrix} x = \begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ \vdots \\ b_n \end{bmatrix}$$

Now, let us take a look at Bariess two examples listed in p. 415 [3].

Example 1.

4.3 Shift

$$\leftarrow$$

4.2 m<sub>3</sub> =  $\frac{24}{-288} = -\frac{1}{12}$

3.3 Shift  $\leftarrow$

144 120 24

3.2 m<sub>2</sub> =  $\frac{30}{-300} = -\frac{1}{10}$

144 120 0 24

2.3 Shift  $\leftarrow$

180 150 120 30 60

2.2 m<sub>2</sub> =  $\frac{40}{-320} = -\frac{1}{8}$

180 150 120 0 30 60

1.3 Shift  $\leftarrow$  240 200 160 120 40 80 120

1.2 m<sub>1</sub> =  $\frac{240}{-360} = -\frac{2}{3}$  240 200 160 120 0 40 80 120

480 360 240 120 240 360 480 600

600 480 360 240 120 240 360 480 600

600 480 360 240 120 240 360 480

1.1 m<sub>-1</sub> =  $\frac{240}{120} = 2$  -360 -240 -120 0 -360 -480 -600 -720

1.3 Shift  $\rightarrow$  -360 -240 -120 -360 -480 -600 -720

2.1 m<sub>-2</sub> =  $\frac{-120}{120} = -1$  -160 -80 0 -320 -400 -480

3.1 m<sub>-3</sub> =  $\frac{-80}{120} = -\frac{2}{3}$  -60 0 -300 -360

3.3 Shift  $\rightarrow$  -60 -300 -360

4.1 m<sub>-4</sub> =  $\frac{-60}{120} = -\frac{1}{2}$  0 -288

4.3 Shift  $\rightarrow$  -60 -728

Hence

$$T^{(-4)} = \begin{bmatrix} 120 & 240 & 360 & 480 & 600 \\ -360 & -480 & -600 & -720 \\ -320 & -400 & -480 \\ & & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ &$$

# The Journal of National Chengchi University Vol. 50, 1984

|                                                                                     | 120                      |                            |                   | 0          |        |       |        |  |

|-------------------------------------------------------------------------------------|--------------------------|----------------------------|-------------------|------------|--------|-------|--------|--|

|                                                                                     | 144<br>180<br>240<br>600 | 120<br>150<br>200<br>480   | 120<br>160<br>360 | 120<br>240 | 120    |       |        |  |

| Example 2.                                                                          |                          |                            |                   |            |        |       |        |  |

| b = 120                                                                             |                          | 30<br>22<br>18<br>20<br>30 |                   |            |        |       |        |  |

| $4.2 \text{ m}_4 = -\frac{1}{12}$                                                   |                          |                            | 120               |            |        |       |        |  |

| $3.2 \text{ m}_3 = -\frac{1}{10}$                                                   |                          |                            | 120               |            | 384    |       |        |  |

| $2.2 \text{ m}_2 = -\frac{1}{8}$                                                    |                          |                            | 240               |            | 390    | 840   |        |  |

| $1.2  \mathrm{m_1} = -\frac{2}{3}$                                                  |                          |                            | 560               |            | 560    | 880   | 1600   |  |

|                                                                                     |                          |                            | 3600              |            | 2640   | 2160  | 2400   |  |

|                                                                                     |                          |                            | 2640              |            | 2160   | 2400  | 3600   |  |

| $1.1 \text{ m}_{-1} = 2$                                                            |                          |                            | -4560             |            | -3120  | -1920 | - 1200 |  |

| 1.3 Shift ←                                                                         | -                        | 4560                       | -3120             |            | - 1920 | -1200 |        |  |

| $2.1 \text{ m}_{-2} = -1$                                                           |                          |                            | - 2560            |            | -1360  | - 320 |        |  |

| 2.3 Shift ←                                                                         | -                        | 2560                       | -1360             |            | -320   |       |        |  |

| $3.1 \text{ m}_{-3} = -\frac{2}{3}$                                                 |                          |                            | -1200             |            | - 60   |       |        |  |

| 3.3 Shift ←                                                                         | -                        | 1200                       | - 60              |            |        |       |        |  |

| $4.1 \text{ m}_{-4} = -\frac{1}{2}$                                                 |                          |                            | 0                 |            |        |       |        |  |

| 4.3 Shift ←                                                                         |                          | 0                          |                   |            |        |       |        |  |

| •                                                                                   |                          | •                          | Q                 | o          | $Q_1$  | $Q_2$ | $Q_3$  |  |

| $ \begin{array}{rcl} 3600 \\ -4560 \\ b^{(-4)} &= -2560 \\ -1200 \\ 0 \end{array} $ |                          |                            |                   |            |        |       |        |  |

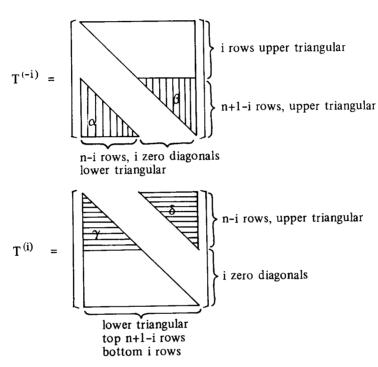

According to Bareiss algorithm Tx = B can be transformed into  $T^{(-1)}x = B^{(-1)}$ .  $T^{(1)}x = B^{(1)}$ ,  $T^{(-2)}x = B^{(-2)}$ ,  $T^{(2)}x = B^{(2)}$ , .....  $T^{(-n)}x = B^{(-n)}$ ,  $T^{(n)}x = B^{(n)}$  and the  $T^{(-n)}$ ;  $T^{(n)}$  are upper and lower triangulars respectively.

Figure 1. Structure of T<sup>(-i)</sup> and T<sup>(i)</sup> in the Bareiss algorithm

We introduce the shift matrices

$$Z_{-i} = (Z_{jk}^{(-i)}) = \delta_{j-k-i}$$

$Z_{i} = (Z_{jk}^{(i)}) = \delta_{j-k+i}$

The effect of premultiplication by  $Z_{-i}$  is to downshift the matrix  $T^{(i-1)}$  by i rows and to replace its first i rows by zeros. Similarly,  $Z_{i}$  upshifts  $T^{(-i)}$  by i rows and replaces its last i rows by zeros. Suppose that the matrix  $T^{(-i+1)}$  has (i-1) null subdiagonals. The following equations show that it will wipe the i-th subdiagonal out without disturbing those already null elements. It follows that the matrix  $T^{(-n)}$  will be upper triangular.

$$T^{(-i)} = T^{(-i+1)} - m_{-i} Z_{-i} T^{(i-1)}, \text{ with } m_{-i} = \frac{t_{i,0}^{(1-i)}}{t_0}$$

$$T^{(i)} = T^{(i-1)} - m_{-i} Z_i T^{(-i)}, \text{ with } m_i = \frac{t_{0,1}^{(i-1)}}{t_{0,n}^{(-i)}}$$

$$B^{(-i)} = B^{(-i+1)} - m_{-i} Z_{-i} B^{(i-1)}$$

$B^{(i)} = B^{(i-1)} - m_{i} Z_{i} B^{(-i)}$

The Bareiss method will not fail as long as all the leading principal submatrices of the given matrix T are nonsingular. An LU-factorization, with L unit lower triangular, of T is then given.

Where

$$T = LU$$

$$L = \frac{1}{t_0} (T^{(n)})^{T2}$$

$$U = T^{(-n)}$$

# 3. New Approach for the Solution

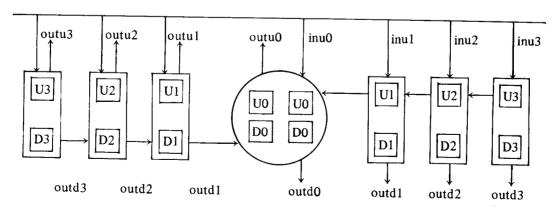

We present here a one-dimensional systolic array for computing the two triangular matices  $T^{(-n)}$  and  $T^{(n)}$ . The array consists of 2n-1 processors  $P_{-n+1}, P_{-n+2}, \ldots$   $P_{-1}, P_0, P_1, \ldots, P_{n-1}$ , arranged from left to right. All processors are identical except for the middle one  $P_0$ . For simplicity we first assume that  $P_0$  can broadcast a scalar quantity to all other processors in constant time. This assumption will soon be dropped. The processor  $P_0$  has four registers  $U_0$ ,  $U_{0+}$ ,  $D_0$ , and  $D_0$ , and each remaining processor  $P_k$  (k not equals to 0) has two registers  $U_k$  and  $D_k$ . We denote the content of register  $P_0$  by  $P_0$ . Each processor has two output lines outuke and outdy, and two input lines inuke and indy. The output line outuke is connected to the input line inuke1, for  $P_0$ , for  $P_0$ ,  $P_0$ ,  $P_0$ ,  $P_0$ , and  $P_0$ , we denote the input line inuke1, for  $P_0$ , and  $P_0$ , and  $P_0$ , we denote the input line inuke1, for  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and  $P_0$ , and  $P_0$ , and each remaining processor  $P_0$  has four registers  $P_0$ , and  $P_0$ , and

Figure 2. The processor array for n = 4

Before iterating, we feed data into the array so that

$$[U_{0-}] = t_0 \qquad [U_{0+}] = t_1,$$

$$[D_{0-}] = t_{-1} \qquad [D_{0+}] = t_0$$

and

$$[U_{-k}] = t_{-k}, \qquad [U_k] = t_{k+1},$$

$$[D_{-k}] = t_{-k-1} \qquad [D_k] = t_k$$

for  $k=1,2,\ldots,n-1$ , we now consider one iteration, say the i-th one. Each iteration consists of three steps. At step one the processor  $P_0$  computes the multiplier

$$m_{-i} = \frac{[D_{0-}]}{[U_{0-}]}$$

This value is broadcast to all processors. Processor  $P_k$ , all k, now computes

$$(i) \equiv [D_k] - m_{-i}[U_k]$$

The quantity  $D_k$ , for  $k \le 0$  is output on line out, and the register  $U_k$  receives the value of (ii). At the third step, we do data transfer. The content of register  $D_k$ , for k-1, is sent to processor  $P_{k+1}$  on line outd. The incoming data for  $P_{k+1}$  is stored in register  $D_{k+1}$ . The content of register  $D_0$  is lost. At the same time, the content of register  $U_k$ , for  $k \ge 1$  is sent to processor  $P_{k-1}$ , on line outu. The incoming data for  $P_{k-1}$  is stored in register  $U_{k-1}$ , and the content of register  $U_0$  is lost. We now disable processors  $P_{-n+1}$  and  $P_{n-1}$ . This completes one iteration of the Bareiss algorithm.

Since we disable the two end processors after each iteration, our method must terminate after n iterations. Let us denote the output on line outd<sub>k</sub> at the i-th iteration by  $d_k^{(i)}$  and the corresponding output on outu<sub>k</sub> by  $u_k^{(i)}$ . The two desired matrices  $T^{(-n)}$  and  $T^{(n)}$  are given by

By transforming the right-hand vector B simultaneously (we will discuss it later). We obtain an upper triangular system  $T^{(-n)}x = B^{(-n)}$  to solve. So  $T^{(n)}$  can be discarded. The Bareiss algorithm appears to require order  $(n^2)$  storage. However, at the expense of some extra computation, we can avoid using more than order (n) storage (the details are presented in the later part of this section too).

We show now that broadcasting is not needed if each processor  $P_k$  (resp.  $P_{-k}$ ), k>0, can pass a scalar quantity to its outer neighbor  $P_{k+1}$  (resp.  $P_{-k-1}$ ) and if  $P_0$ can pass a number to both  $P_1$  and  $P_{-1}$ . Let us describe how the i-th iteration (say) proceeds. The middle processor  $P_0$  reads the inputs on lines inu $_0$  and ind $_0$ , and stores the numbers in registers  $U_{0+}$  and  $D_{0-}$ , respectively. The computing starts with  $P_0$  calculating the multiplier  $m_{-i}$  and passes the value to its two neighbors  $P_{-1}$ and P<sub>1</sub>. The processor P<sub>0</sub> now performs the second step of the iteration by computing the multiplier  $m_i$  and again passes its value to processors  $P_{-1}$  and  $P_1$ . The processor  $P_1$  (resp.  $P_{-1}$ ), on receiving  $m_{-i}$ , will do the computation and pass the multiplier to the neighbor  $P_2$  (resp.  $P_{-2}$ ). Then  $P_1$  (resp.  $P_{-1}$ ) will receive the multiplier m<sub>i</sub>. The operations are now performed and the value of m<sub>i</sub> will be passed to processor  $P_2$  (resp.  $P_{-2}$ ). The processor  $P_1$  (resp.  $P_{-1}$ ) completes its share of the iteration by sending the content of register U<sub>1</sub> (resp. D<sub>-1</sub>) leftward (resp. rightward) to processor  $P_0$ . The processors  $P_2$  and  $P_{-2}$  on receiving the multipliers  $m_{-i}$  and then m<sub>i</sub>, will perform the necessary computations, the passing on of the multipliers and finally the shifting of the necessary information toward the middle processor.

This process expands outward until the two end processors  $P_{n-i}$  and  $P_{-n+i}$  have done their tasks, ending the iteration. An important observation here is that the (i+1)-st iteration can start as soon as processor  $P_0$  receives the data from its two neighbors. Our technique for avoiding broadcast is quite common: processors are active only on alternate time steps  $(P_0, P_{+2}, \ldots)$  at time  $\tau = 1, 3, \ldots$  and  $P_{\pm 1}, P_{\pm 3}, \ldots$

at time  $\tau = 2, 4...$ ), and the operations of processors  $P_{\pm k}$  are delayed by k time steps relative to the operation of processor  $P_0$ .

Suppose that the given matrix T is banded with half-bandwidth w. We can, of course, disregard this special structure and still use 2n-1 processors. But as processors  $P_{\pm(w-1)}$ ,  $P_{\pm w}$ , ...  $P_{\pm(n-1)}$  work only with null data, we may perform the elimination using only 2w-3 processors if the input lines inu $_{w-2}$  and ind $_{-w+2}$  always carry the number zero. We will disable the processors  $P_{n-i}$  and  $P_{-n+i}$  at the end of the i-th iteration, for i=n-w+2, n-w+3, .... n-1.

Now let us look back to Bareiss example 1.

Note that T = LU, where  $U = T^{(-4)}$  and

$$L = \frac{1}{120} (T^{(4)})^{T2} = 3 \quad \frac{4}{3} \quad 1$$

$$4 \quad \frac{5}{3} \quad \frac{5}{4} \quad 1$$

$$5 \quad 2 \quad \frac{3}{2} \quad \frac{6}{5} \quad 1$$

Suppose that we want to find the vector  $B^{(-n)}$  that satisfies  $T^{(-n)}x = B^{(-n)}$  then we have to do the following steps that is what we have mentioned before, modifying the right-hand vector.

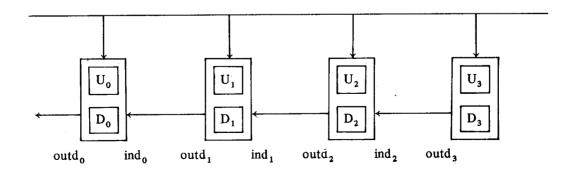

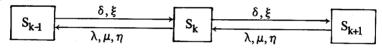

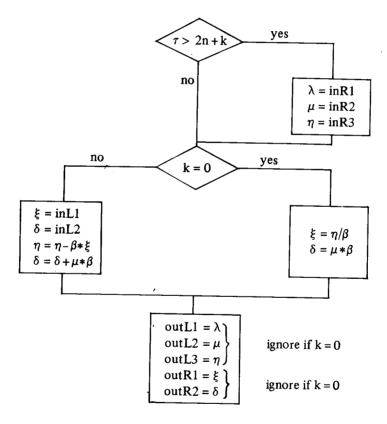

The structure and the operations of the systolic array are very similar to the right-half of the systolic architecture of the previous section. The array here consists of the n processors  $Q_0, Q_1, \ldots, Q_{n-1}$ . All the processors are identical.

Figure 3. Systolic array for finding  $B^{(-n)}$  (n = 4)

Each  $Q_k$  has two registers  $U_k$  and  $D_k$ , one output line outd<sub>k</sub> and one input line ind<sub>k</sub>. The lines ind<sub>k</sub> and outd<sub>k+1</sub> are connected (for  $k=0,1,\ldots,n-2$ ). We also assume temporarily that all processors can receive the broadcast of a scalar quantity.

Before iteration starts, data are fed into the processors so that, for  $k = 0, 1, \ldots, n-1$ ,

$$[U_k] = B_k$$

$$[D_k] = B_{k+1}$$

where  $B = (b_0, b_1, \dots, b_n)^T$ . Let us consider the i-th iteration, where  $i \ge 1$ . An iteration consists of three steps, same as in the previous section. At the first step, the multiplier  $m_{-i}$  arrives at processor  $Q_k$ , which then computes

(iii)

$$\equiv [D_k] - m_{-i}[U_k]$$

and stores (iii) in register  $D_k$ . The second step begins when  $Q_k$  receives the multiplier  $m_i$ . It computes

$$(iv) \equiv [U_k] - m_i[D_k]$$

and stores the result in  $U_k$ . The third step is now initiated. It involves a transfer of the content of register  $D_k$  from processor  $Q_k$  to processor  $Q_{k-1}$ , for  $k \ge 1$ . The content of  $D_1$  is sent out on  $\operatorname{outd}_0$  and register  $D_k$ , for  $k \ge 0$ , receives the content of register  $D_{k+1}$ . The completion of the data transfer ends the i-th iteration and processor  $Q_{n-i}$  is disabled. If we denote the output on line  $\operatorname{outd}_0$  after the i-th iteration by  $d_0^{(k)}$ , then the vector  $B^{(-n)}$  is given by

Since the algorithms in this and the previous sections are very similar, we can argue using the same reasonings as before that broadcasting is unnecessary if each processor  $\mathbf{Q}_k$  can pass the multiplier to its right neighbor  $\mathbf{Q}_{k+1}$  and if the operation of processor  $\mathbf{Q}_k$  is delayed by k time steps relative to the operation of processor  $\mathbf{Q}_0$ .

And now let us refer back to Bareiss example 2.

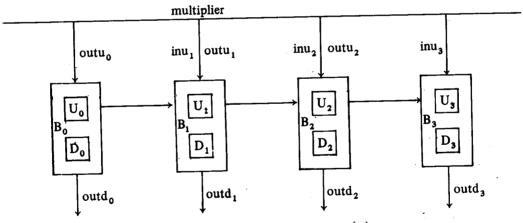

We consider the regeneration of the upper triangular matrix  $T^{(-n)}$  using only its last column and the 2n multipliers  $m_{\pm i}$ . Our key idea is to run the elimination algorithm in the previous part of this section:

$$\begin{split} T^{(i-1)} &= T^{(i)} + m_i Z_i T^{(-i)}, \\ T^{(-i+1)} &= T^{(-i)} + m_{-i} Z_{-i} T^{(i-1)}, \end{split}$$

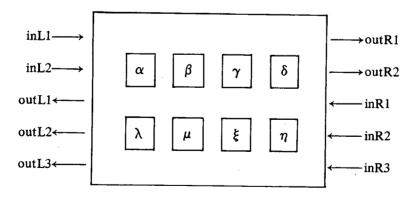

for  $i=n, n-1, \ldots, 1$ . (Observe that rows 0 to i for  $T^{(-n)}$  are equal to rows 0 to i of  $T^{(-i)}$ ). So our systolic array consists of n identical processors  $B_0, B_1, \ldots, B_{n-1}$ . Each processor  $B_k$  has two registers  $U_k$  and  $D_k$ . Initially.

$$[U_k] = 0$$

, and  $[D_k] = t_{n-k,n}^{(-n)}$ ,

for  $k=0,1,\ldots,n-1$ . We again assume for a moment that there is a broadcasting mechanism. Each processor  $B_k$  has two output lines outu<sub>k</sub> and outd<sub>k</sub> and one input line inu<sub>k</sub>. The lines outu<sub>k</sub> and inu<sub>k+1</sub> are connected, for  $k \ge 0$ .

Figure 4. A systolic array for generating  $T^{(-n)}$  (n = 4)

Only one processor,  $B_0$ , is active for the initial iteration. At the end of the i-th iteration,  $i \ge 1$ , processor  $B_i$  is activated for subsequent computations so that the (i+1) processors  $B_0$ ,  $B_1$ , ...,  $B_i$  are active during the (i+1)-st iteration. Each iteration consists of three steps. Let us describe the i-th iteration. At the first step, the multiplier  $m_{n+1-i}$  is broadcast to all the processors and the following computation is done:

$$(v) \equiv [U_k] + m_{n+1-i}[D_k],$$

for  $k=0,1,\ldots,i-1$ . The result (v) is stored in register  $U_k$ . The second step starts when the multiplier  $m_{-n-1+i}$  is broadcast to all processors. Processor  $B_k$   $(0 \le k \le i-1)$  then computes

$$(vi) \equiv [D_k] + m_{-n-1+i}[U_k],$$

outputs the result (vi) on outd<sub>k</sub> and also stores the number in register  $D_k$ . The third step is put a shifting of the content of register  $U_k$  to register  $U_{k+1}$ , for  $k=0,1,\ldots$ , i-1. Register  $U_0$  will contain the number zero. The complete procedure stops after n iterations.

If we denote the output on line  $\operatorname{outd}_k$  at the i-th iteration by  $d_k^{(i)}$ , the desired matrix  $T^{(-n)}$  is given by

As before, we can argue that broadcasting is unnecessary as long as each processor can pass a scalar quantity to its right neighbor.

Since our primary concern is the solution of  $T^{(-n)}x = B^{(-n)}$  on a linear systolic array, it is interesting to note that we have regenerated the elements of  $T^{(-n)}$  in the exact order as required by the Kung-Leiserson algorithm for back substitution.

4.3 shift

$$\rightarrow$$

4.1 m<sub>1</sub> =  $-\frac{2}{3}$

240 350 480 600

3.3 shift  $\rightarrow$

3.1 m<sub>2</sub> =  $-\frac{1}{8}$

40 80 120

2.3 shift  $\rightarrow$

0 30 60

# 4. A Proposed Model

We can construct one systolic array that solves the given equations Tx = B. Because of the similarities in their operations, processors  $P_{\pm k}$  and  $Q_k$   $(k \ge 0)$  are combined into one super-processor  $S_k$   $(k \ge 0)$ . We then program  $S_k$   $(k \ge 0)$  to do the regeneration of  $T^{(-n)}$  and the solution of  $T^{(-n)}x = B^{(-n)}$ . Let us describe our linear array of n+1 super-processors  $S_0$ ,  $S_1$ , ...,  $S_n$ . (The last processor  $S_n$  is needed for the back substitution). In the Bareiss algorithm four triangular matrices.

$$\alpha = \begin{bmatrix} \alpha_0 & 0 \\ \alpha_1 & \alpha_0 \end{bmatrix} \qquad \beta = \begin{bmatrix} \beta_0 & \beta_1 \\ 0 & \beta_0 \end{bmatrix}$$

$$\gamma = \begin{bmatrix} \gamma_0 & 0 \\ \gamma_1 & \gamma_0 \end{bmatrix} \qquad \delta = \begin{bmatrix} \delta_0 & \delta_1 \\ 0 & \delta_0 \end{bmatrix}$$

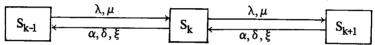

are updated (see Figure 1). Now each processor  $S_k$  has registers to store  $\alpha_k$ ,  $\beta_k$ ,  $\gamma_k$  and  $\delta_k$ . (When describing processor  $S_k$  we shall omit the subscripts and simply refer to registers  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\delta$ .) Processor  $S_k$  requires four additional registers  $\lambda_k$  for a multiplier  $m_{-j}$ ,  $\mu_k$  for a multiplier  $m_{+j}$ , and  $\xi_k$  and  $\eta_k$  which are associated with the right-hand side vector B and the solution x.

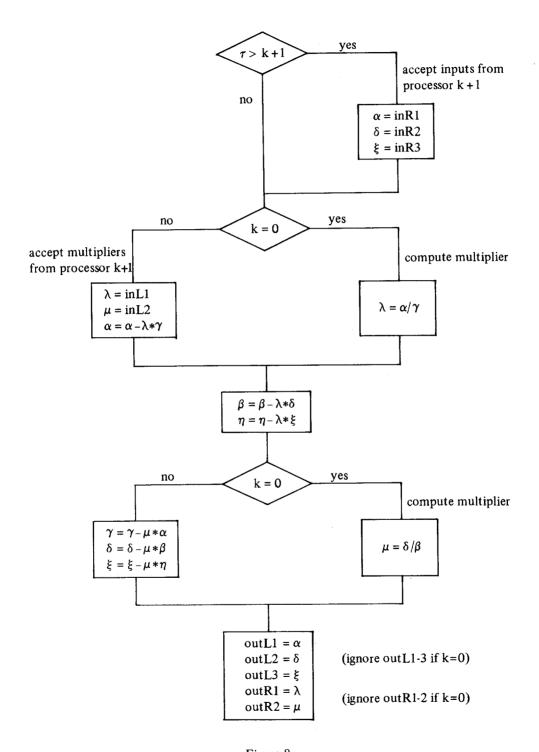

Data flows in both directions between adjacent processors, as shown in Figure 5. Hence, each processor needs five input and five output data paths denoted by inL1, inL2, inR1, inR2, inR3, outL1, outL2, outL3, outR1, and outR2 (see Figure 6).

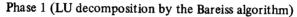

Phase 2 (Back substitution to solve triangular system)

Figure 5. Data flow for systolic system solver.

Figure 6. Systolic processor for systems.

Initialization is as follows:  $\alpha_k := t_{-(k+1)}$ ;  $\beta_k := t_k$ ;  $\gamma_k := t_{-k}$ ;  $\delta_k := t_{k+1}$ ;  $\lambda_k := 0$ ;  $\mu_k := 0$ ;  $\xi_k := b_{n-k-1}$ ;  $\eta_k := b_{n-k}$ ; all for  $0 \le k \le n$  (we assume that  $t_{-(n+1)} = t_{n+1} = b_{-1} = 0$  to cover end-conditions). Clearly this can be done in time order(n) if T and B

$\begin{array}{c|c}

\hline

& \text{odd} & \\

\hline

& \tau > k & \\

\hline

& \tau > 2n + k & \\

\hline

& \tau > 2n + k & \\

\hline

& \tau > 2n + k & \\

\hline

& \tau < 4n - k & \\

\hline

& Phase 2-back \\

& Substitution \\

& (see Figure 8) & \\

\hline

& (see Figure 9) & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 4n - k & \\

\hline

& \tau < 7n - k & \\

\hline

& \tau < 7n - k & \\

\hline$

Program for processor k at time step  $\tau$ ,  $0 \le k \le n$ ,  $1 \le \tau \le 4n$

Figure 7. Systolic processor for equation solver.

are available at either end of the systolic array.

We present the program executed by processor  $S_k$   $(0 \le k \le n)$  at time step  $\tau(1 \le \tau \le 4n)$  in Figure 7. The final solution x is given by  $x_k = \xi_k$ , where  $\xi_k$  is stored in register  $\xi$  of processor  $S_k$  after step 4n. What follows are some observations concerning the program:

- 1. Processor  $S_k$  is active only if  $k < \tau < 2n-k$  (Phase 1) or  $2n+k \le \tau \le 4n-k$  (Phase 2). It is assumed that  $S_k$  knows its index k and the current value of  $\tau$  (though this could be avoided by the use of 1-bit systolic control paths).

- 2. Pairs of adjacent processors could be combined. Since only one processor of each pair is active at each time step. This would increase the mean processor utilization from 25% to 50% (see observation 1 above).

- 3. Processor  $S_0$  performs floating-point divisions, other processors perform only additions and multiplications. A time step has to be long enough for six floating-point additions and multiplications, plus data transfers, during Phase 1 (less during Phase 2).

- 4. The Bareiss algorithm requires  $4 \cdot 5n^2$  multiplications as given, but a simple modification (transmitting  $1+\lambda\mu$ ) will give time 4n if have  $[\frac{n}{2}]$  processors (see ob-

Figure 8.

servation 2), each with six multiply-add units. The corresponding figures for the symmetric Bareiss algorithm for symmetric matrices are  $4n^2$  4n, and 5.

- 5. An alternative for Phase 2 is the use of the Gohberg-semencul formula. But the formula is more expensive in terms of both operations and time, and it also fails to take advantage of the possible band structure of the matrix.

- 6. Processor  $S_k$  typically reads its input lines  $inL1, \ldots, inR3$ , does some floating-point computations, and writes to its output lines  $outL1, \ldots, outR2$ . Hence, pairs of input and output lines could be combined into single bidirectional lines (e.g. inL1 and outL1 could be combined).

Figure 9.

# 5. Acknowledgement

The author would like to thank Dr. Fong-Ching Lin, Associate Professor of the Department of Information Engineering of National Taiwan University, for pointing out the references; Dr. Chuang-Ching Song, Associate Professor of the Department of Applied Mathematics of National Chengchi University, for helping me solve some of the mathematical problems during this study and Dr. Dale Bremmer, Associate Professor of the Engineering Technology of Texas A&M, for sending me all the information I requested.

### 6. References

- 1. H.T. Kung and C.E. Leiserson, Systolic Arrays (For VLSI) April, 1978, 201-223.

- 2. H.T. Kung, Let's Design Algorithms for VLSI Systems Jan., 1979, 115-125.

- 3. E.H. Bareiss, Numberical Solution of Linear Equations with Toeplitz and Vector Toeplitz Matrices, Numer. Math., 13(1969), 404-424.

- 4. H.T. Kung and C.E. Leiserson, Algorithms for VLSI Processors Arrays in Introduction to VLSI Systems, 1980, 180-208.

- S.Y. Kung, Impact of VLSI of Modern Signal Processing, Proc, USC Workshop on VLSI and Modern Signal Processing, Los Angeles, Ca (November 1982), 123-132.